by Mat Dirjish

At the 2026 International Solid-State Circuits Conference (ISSCC), CEA-List and CEA-Leti demonstrated what they claim is the first electro-optical router with dynamic, frame-level optical routing with integral CMOS control logic. They believe this is a major step toward practical optical networking inside advanced chiplet-based packages.

A paper titled “A 3.19pJ/bit Electro-Optical Router with 18ns Setup Frame-Level Routing and 1-6 Wavelength Flexible Link Capacity for Photonic Interposers” demonstrates an electro-optical router implemented in 28-nm CMOS on a photonic interposer, reportedly capable of establishing optical paths in 18 ns. It dynamically selects one-to-six wavelengths per link, and achieves an energy efficiency of 3.19 pJ/bit with an active area of 0.007 mm² per link.

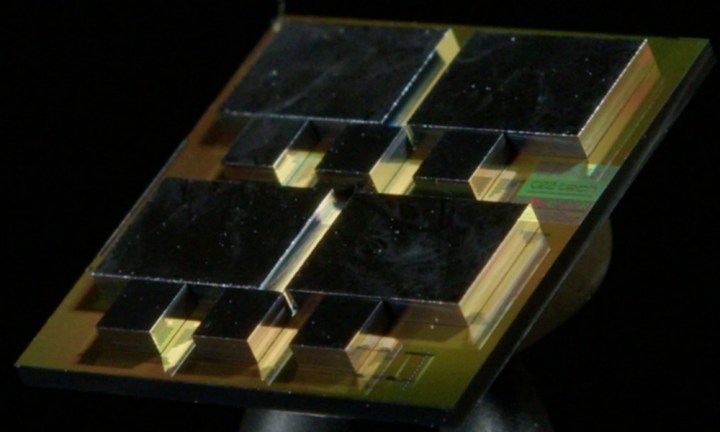

Detail view of the system-on-interposer, with a companion electro-optical router for each computing die and two additional routers for primary IO. Light coupling to the optical network on interposer is achieved on fiber coupling visible on the bottom-right corner.

The researchers explain that current optical interconnects provide initialization and training times ranging from microseconds to milliseconds. These latencies prevent the use of optical links as true networking fabrics inside multi-die packages. The 3.19pJ/bit electro-optical router addresses this limitation by integrating optical switching, routing control, serializer/deserializer (SerDes), and clocking logic directly within silicon photonics. The result is a routed optical interconnect that operates at nanosecond timescales, enabling optical communication across centimeter-scale interposers with responsiveness previously limited to short electrical links.

The router prototype is reportedly the first demonstration of dynamic optical routing in an integrated photonic switch that includes CMOS logic up to the protocol level. The researchers say previous optical switch demonstrations rely on standalone photonic devices with static or slowly reconfigured paths and do not integrate the necessary drive, control, and routing logic for packet-level operation.

The router operates as a miniature network switch inside the package, combining micro-ring-based photonic devices with digital control logic to move data across the interposer. This approach avoids power and latency penalties that scale with distance, thereby relaxing constraints on data locality and enabling flexible hardware architectures and software data placement.

The researchers conclude that, by bringing ultra-low-latency optical networking into the package, the technology opens possibilities for high-performance computing, AI accelerators, and data-intensive systems, in which greater model sizes and memory demands stress conventional interconnects. As an alternative to forcing data to reside near compute cores to minimize electrical routing costs, dynamically routed optical links allow designers to treat memory and compute resources across the interposer as part of a unified, high-reach fabric without sacrificing latency or energy efficiency.

CEA-List’s Yvain Thonnart explains, “As chiplet systems continue to grow in scale and complexity, the ability to move data efficiently across the entire package becomes essential. Our goal was to demonstrate that photonic links can provide that reach without sacrificing the flexibility designers expect from modern interconnects. This router is a step toward practical, dynamically routed optical networks that fit within standard CMOS design flows and real product constraints.”